# PIP-II Beam Pattern Generator Upgrade

P. Varghese\*, H. Shukla, S. Raman, D. Klepec, Fermilab, Batavia, IL, USA J. Dusatko, D. Chabot, SLAC, Menlo Park, CA, USA

ID 26

#### Introduction

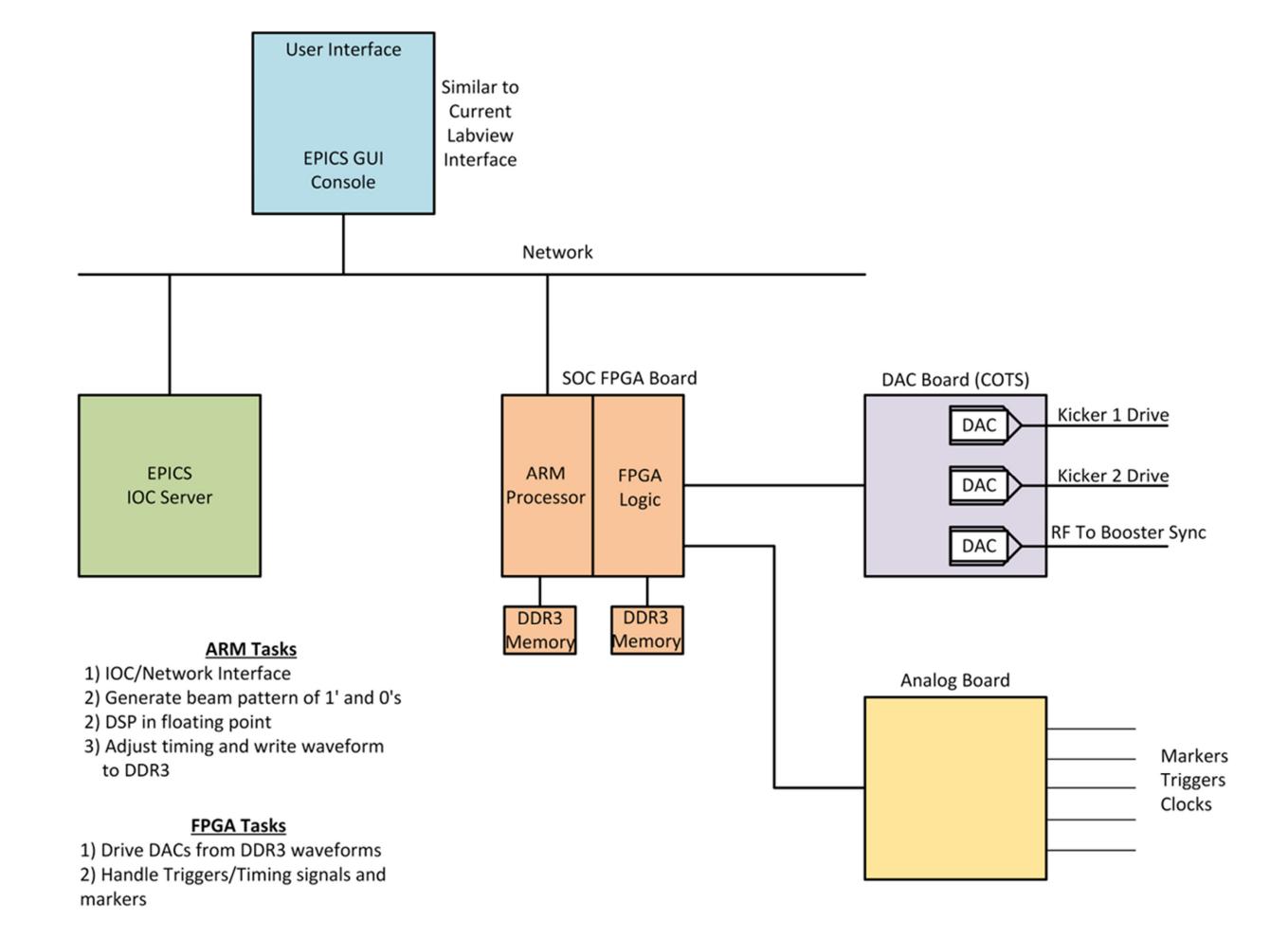

A prototype beam pattern generator for the PIP-II Linac testing used Labview and an external server for the pattern generation. A new design using a COTS sourced SoCFPGA and a DAC board offers the advantages of low hardware and development cost. The pattern generation, digital signal processing and the interface to an external EPICS server are integrated into the ARM processor of the FPGA. The system design is described and the test results are presented.

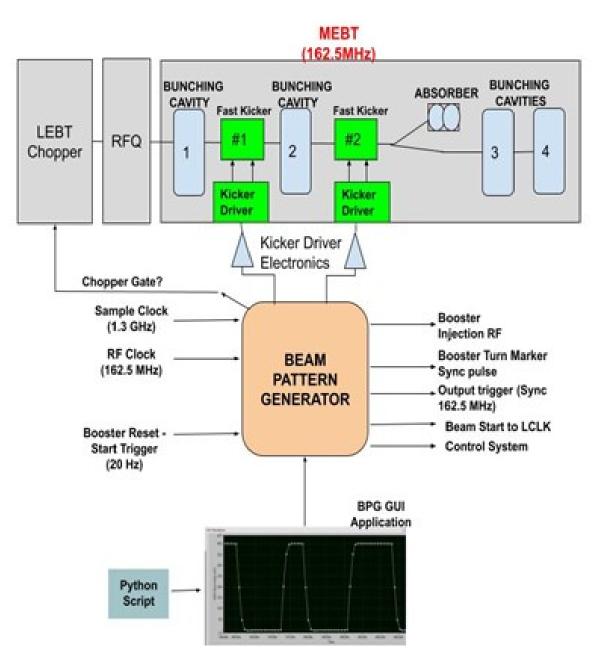

## **BPG Prototype**

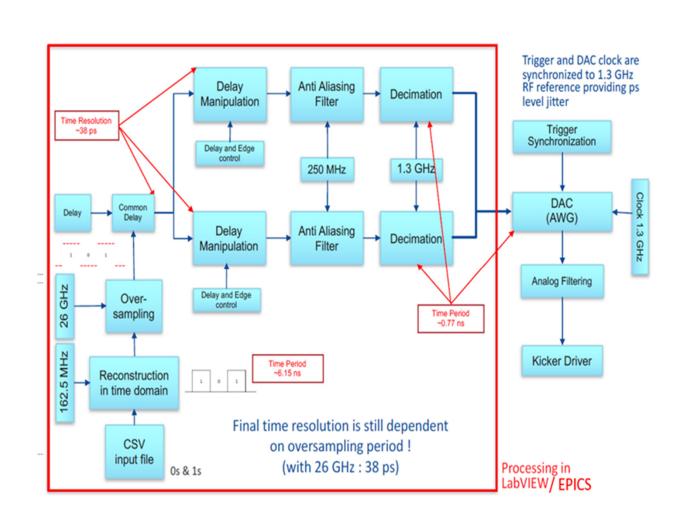

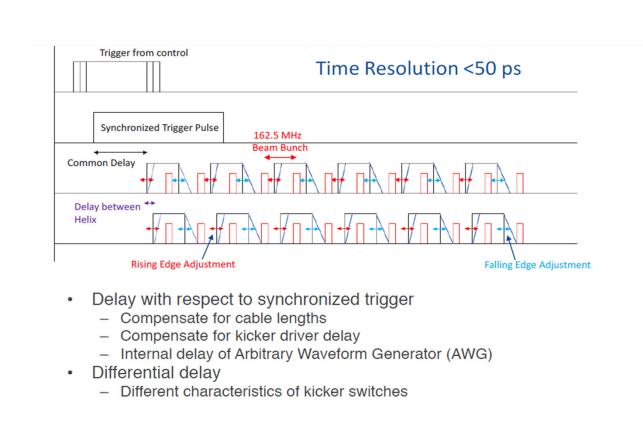

# Signal Processing and Delay Adjustment

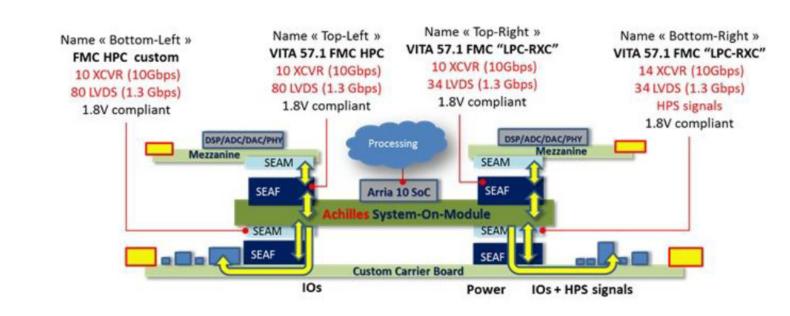

# **BPG Upgrade Architectuure**

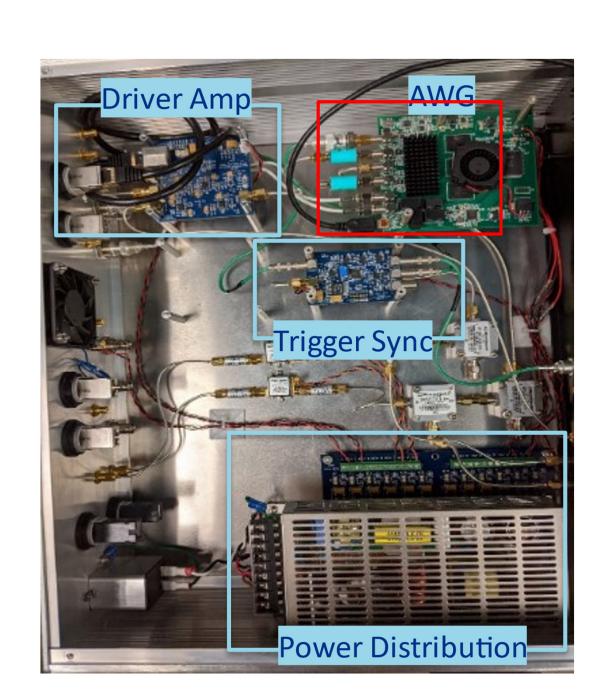

## **Hardware Components**

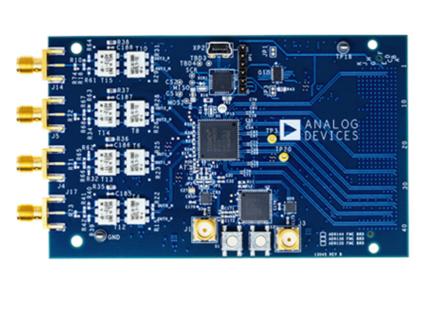

AD9172-FMCEBZ

16-bit, 12.6 GSPS, Ext Clk Input

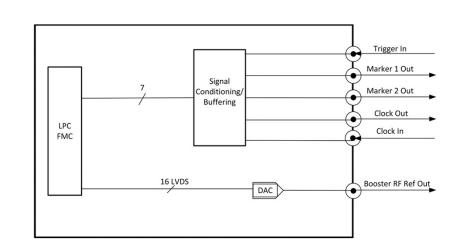

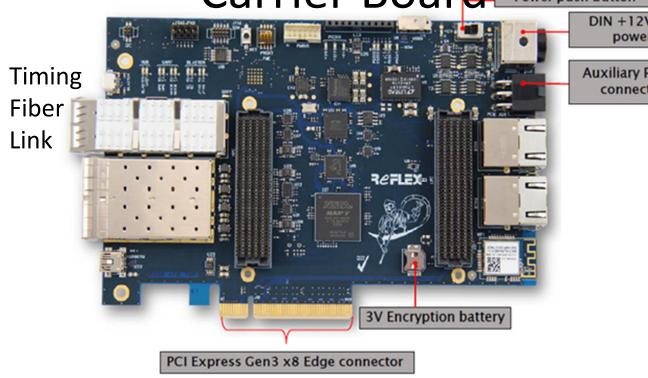

FMC Analog PCB Arria10 SOM

DAC Board – Multiple Choices Carrier Board Power push button

#### Hardware Configuration

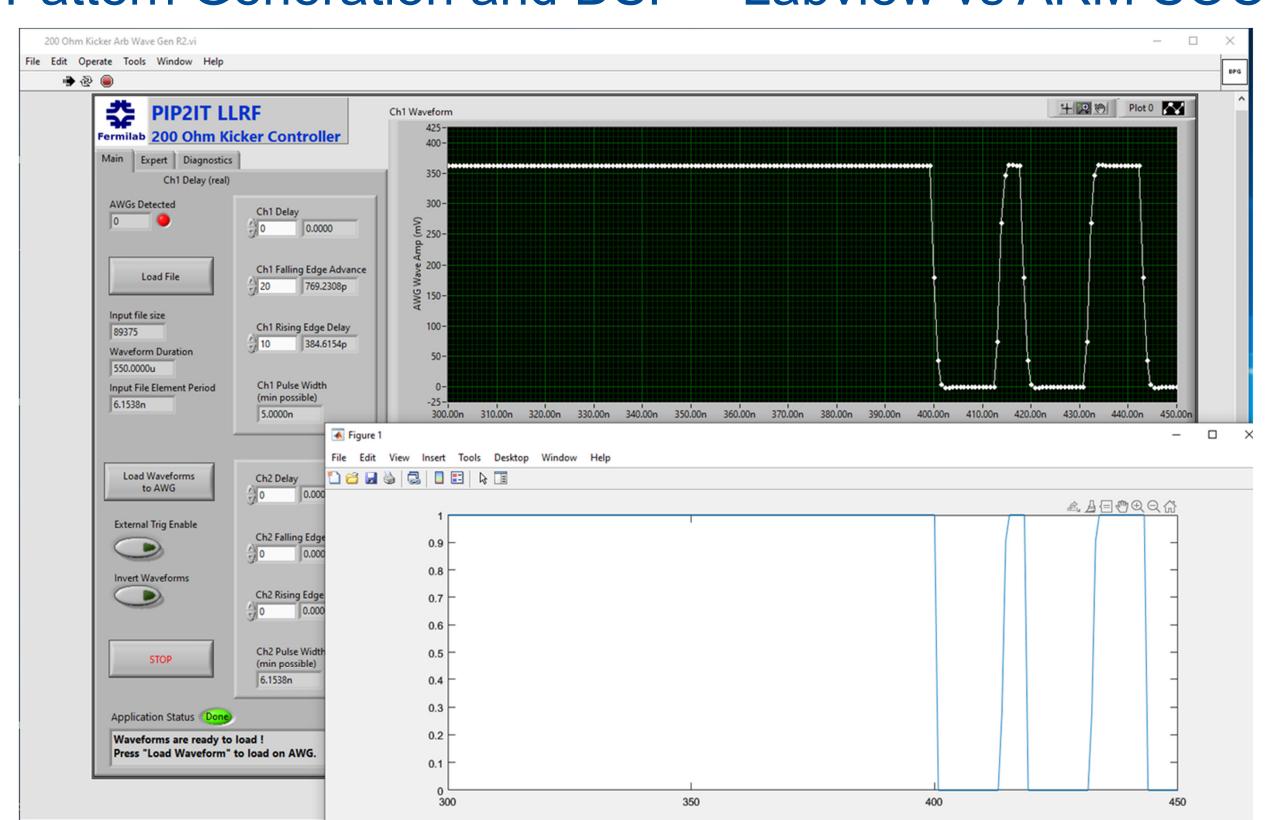

#### Pattern Generation and DSP – Labview vs ARM SOC

#### DAC Output Prototype

### DAC Output SOCFPGA

## Summary

- Major technical aspects for the upgrade already studied and demonstrated to work

- Tested Performance with prototype is guaranteed since the signal processing implemented is the same used at PIP2IT

- This upgrade is a joint project with SLAC